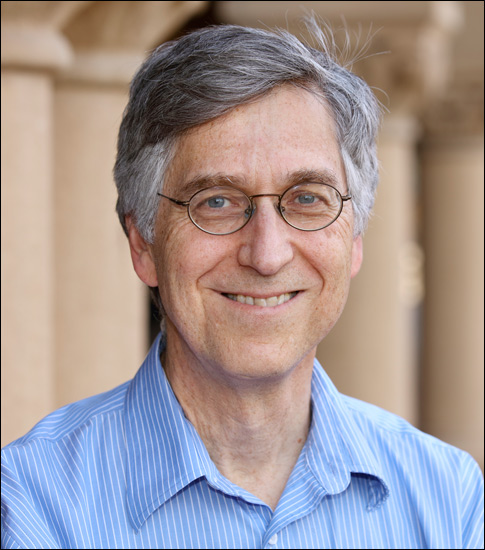

ACM and IEEE Computer Society named Mark Horowitz, a Professor at Stanford University, as the recipient of the 2022 Eckert-Mauchly Award for contributions to microprocessor memory systems. Horowitz was the first to identify the processor to dynamic random-access memory (DRAM) interface as a key bottleneck that required architecture and circuit optimization. He pioneered high-bandwidth DRAM interfaces. In addition, modern DRAM interfaces such as SDDR and LPDDR were strongly influenced by his techniques.

Horowitz was also a major contributor to the DASH and FLASH projects, which explored scalable methods for implementing cache coherency using directories rather than snooping protocols. Today almost all cache-coherent multiprocessors rely on such directory mechanisms either within or across multicores. Horowitz has led research that recognizes that future performance/energy progress after the end of Dennard scaling will require greater use of hardware accelerators, and pioneered work in Smart Memories, an early work customizing memory as well as processors; many of today’s domain-specific architectures build on this concept. He is a Fellow of ACM, IEEE, and the American Academy of Arts and Sciences, and he is a Member of the National Academy of Engineering.

Horowitz will be formally presented with the award at the ACM/IEEE International Symposium on Computer Architecture (ISCA) being held June 18–22 in New York City.

ACM and IEEE Computer Society co-sponsor the Eckert-Mauchly Award, which was initiated in 1979. It recognizes contributions to computer and digital systems architecture and comes with a $5,000 prize. The award was named for John Presper Eckert and John William Mauchly, who collaborated on the design and construction of the Electronic Numerical Integrator and Computer (ENIAC), the pioneering large-scale electronic computing machine, which was completed in 1947.